- 您现在的位置:买卖IC网 > Sheet目录1245 > SOUNDBITE (Freescale Semiconductor)BOARD DEMO AUDIO DEVELOPMENT

�� �

�

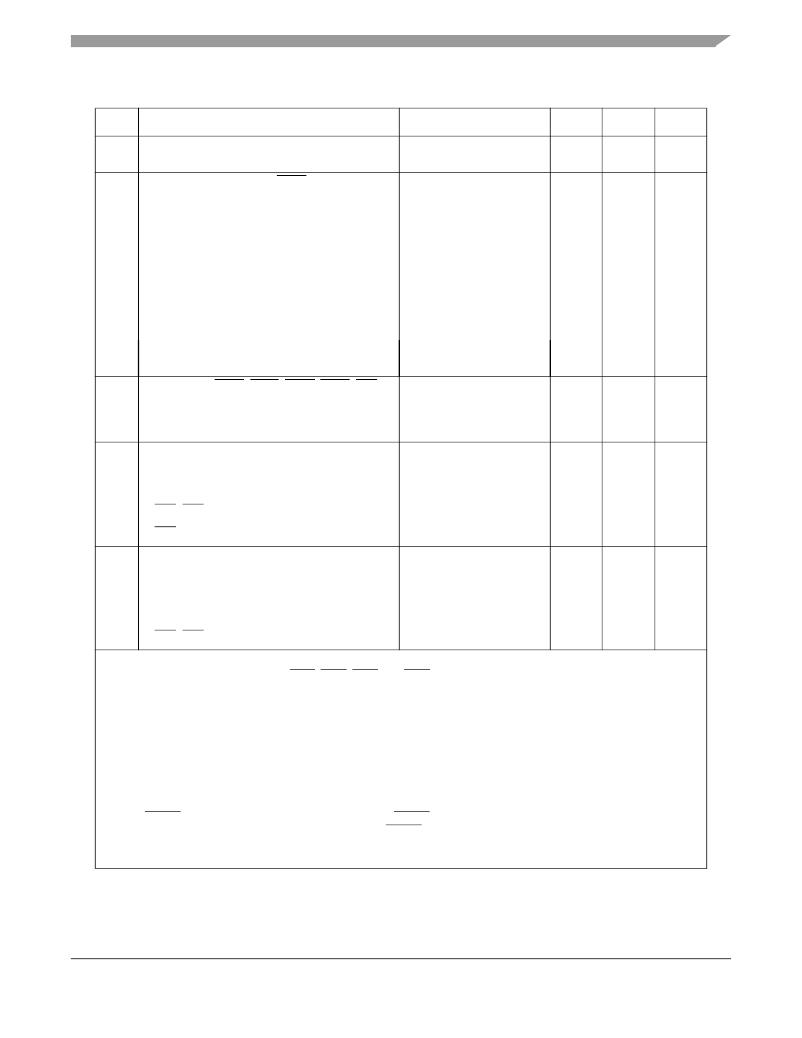

Reset,� Stop,� Mode� Select,� and� Interrupt� Timing�

�Table� 19.� Reset,� Stop,� Mode� Select,� and� Interrupt� Timing� (continued)�

�No.�

�18�

�Characteristics�

�Delay� from� interrupt� trigger� to� interrupt� code�

�Expression�

�10� xT� C� +� 5�

�Min�

�60.0�

�Max�

�Unit�

�ns�

�execution.�

�19�

�Duration� of� level� sensitive� IRQA� assertion� to�

�ensure� interrupt� service� (when� exiting� Stop)� 2,� 3�

�?� PLL� is� active� during� Stop� and� Stop� delay� is�

�enabled�

�9+(128K� � T� C)�

�704�

�—�

�us�

�(OMR� Bit� 6� =� 0)�

�?� PLL� is� active� during� Stop� and� Stop� delay� is� not�

�25� � T� C�

�138�

�—�

�ns�

�enabled�

�(OMR� Bit� 6� =� 1)�

�?� PLL� is� not� active� during� Stop� and� Stop� delay� is�

�9+(128KxT� C� )+T� lock�

�5.7�

�ms�

�enabled� (OMR� Bit� 6� =� 0)�

�?� PLL� is� not� active� during� Stop� and� Stop� delay� is�

�(25� x� T� C� )+T� lock�

�5�

�ms�

�not� enabled� (OMR� Bit� 6� =� 1)�

�20�

�?� Delay� from� IRQA,� IRQB,� IRQC,� IRQD,� NMI�

�10� x� T� C� +� 3.0�

�59.0�

�ns�

�assertion� to� general-purpose� transfer� output�

�valid� caused� by� first� interrupt� instruction�

�execution�

�21�

�Interrupt� Requests� Rate�

�?� ESAI,� ESAI_1,� SHI,� DAX,� Timer�

�?� DMA�

�?� IRQ,� NMI� (edge� trigger)�

�?� IRQ� (level� trigger)�

�12� x� T� C�

�8� x� T� C�

�8� x� T� C�

�12� c� T� C�

�—�

�—�

�—�

�—�

�—�

�—�

�—�

�—�

�ns�

�ns�

�ns�

�ns�

�22�

�DMA� Requests� Rate�

�?� Data� read� from� ESAI,� ESAI_1,� SHI,� DAX�

�?� Data� write� to� ESAI,� ESAI_1,� SHI,� DAX�

�?� Timer�

�?� IRQ,� NMI� (edge� trigger)�

�6� x� T� C�

�7� x� T� C�

�2� x� T� C�

�3� x� T� C�

�—�

�—�

�—�

�—�

�—�

�—�

�—�

�—�

�ns�

�ns�

�ns�

�ns�

�Note:�

�1.� When� using� fast� interrupts� and� IRQA,� IRQB,� IRQC,� and� IRQD� are� defined� as� level-sensitive,� timings� 19� through� 21� apply�

�to� prevent� multiple� interrupt� service.� To� avoid� these� timing� restrictions,� the� deasserted� Edge-triggered� mode� is�

�recommended� when� using� fast� interrupts.� Long� interrupts� are� recommended� when� using� Level-sensitive� mode.�

�2.� For� PLL� disable,� using� external� clock� (PCTL� Bit� 13� =� 0),� no� stabilization� delay� is� required� and� recovery� time� will� be�

�defined� by� the� OMR� Bit� 6� settings.�

�For� PLL� enable,� (if� bit� 12� of� the� PCTL� register� is� 0),� the� PLL� is� shutdown� during� Stop.� Recovering� from� Stop� requires� the�

�PLL� to� get� locked.� The� PLL� lock� procedure� duration,� PLL� Lock� Cycles� (PLC),� may� be� in� the� range� of� 0.5� ms.�

�3.� Periodically� sampled� and� not� 100%� tested�

�4.� RESET� duration� is� measured� during� the� time� in� which� RESET� is� asserted,� V� DD� is� valid,� and� the� EXTAL� input� is� active� and�

�valid.� When� the� V� DD� is� valid,� but� the� other� “required� RESET� duration”� conditions� (as� specified� above)� have� not� been� yet�

�met,� the� device� circuitry� will� be� in� an� uninitialized� state� that� can� result� in� significant� power� consumption� and� heat-up.�

�Designs� should� minimize� this� state� to� the� shortest� possible� duration.�

�DSP56371� Data� Sheet,� Rev.� 4.1�

�Freescale� Semiconductor�

�39�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SP339EER1-0A-EB

BOARD EVALUATION FOR SP339E

SP720ABG

TVS ARRAY ESD 14 INPUT 16-SOIC

SP720ABT

TVS ARRAY ESD 14 INPUT 16-SOIC

SP721ABG

TVS ARRAY ESD 6 INPUT 8-SOIC

SP721ABT

TVS ARRAY ESD 6 INPUT 8-SOIC

SP723ABT

TVS ARRAY ESD 6 INPUT 8-SOIC

SP723APP

TVS ARRAY ESD 6 INPUT 8-DIP

SP724AHTG

TVS ARRAY ESD 4 INPUT SOT-23

相关代理商/技术参数

SOURCE INSPECTION

制造商:Vishay Dale 功能描述:FACTORY INSPECTION

SOURCE INSPECTION CHARGE

制造商:Leach International Corporation 功能描述:SUB MINIATURE - Virtual or Non-Physical Inventory (Software & Literature)

SOURCEINSPECTION/SG1549Y-12824

制造商:Microsemi Corporation 功能描述:CURRENT SENSE LATCH - Bulk

SOVEREIGN 10-300

制造商:Fane International 功能描述:Sovereign Series 10" Professional Audio Woofer - 300W RMS

SOVEREIGN 12-200

制造商:Fane International 功能描述:Sovereign Series 12 Inch Prosound Woofer 200W

SOVEREIGN 15-250

制造商:Fane International 功能描述:Sovereign Series 15 Inch Prosound Woofer

SOVEREIGN 15-500

制造商:Fane International 功能描述:Sovereign Series 15 Inch Prosound Woofer 500W

SOVEREIGN 18-500

制造商:Fane International 功能描述:Sovereign Series 18 Inch Prosound Woofer